Researchers at the University of Osaka have demonstrated a new way to create three-dimensional interconnections of integrated circuits that operate at short temperatures and do not require external pressure, which could lead to cheap and energy-efficient electronics.

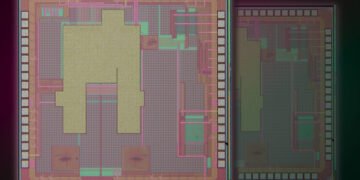

Researchers at the University of Osaka’s Flexible 3D-System Integration Laboratory have developed a new method of directly three-dimensionally connecting copper electrodes with silver, which can reduce the cost and energy (cheap and energy-efficient electronics ) required of new electronic equipment. This work can help design next-generation smart devices that are more compact and use less energy. Three-dimensional integrated circuits are playing an increasingly important role in electronic devices. Compared to conventional 2D circuits, this architecture saves the same space and reduces the material required for the connecting wires. However, the ability to create reliable 3D connections requires new methods compared to the advanced technologies used for conventional integrated circuits.

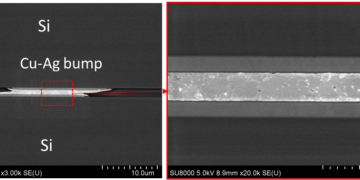

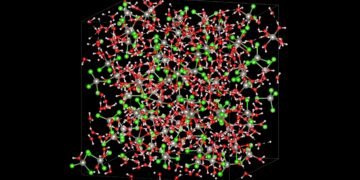

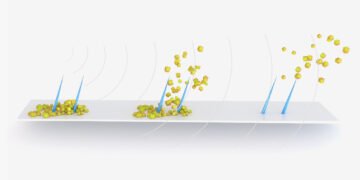

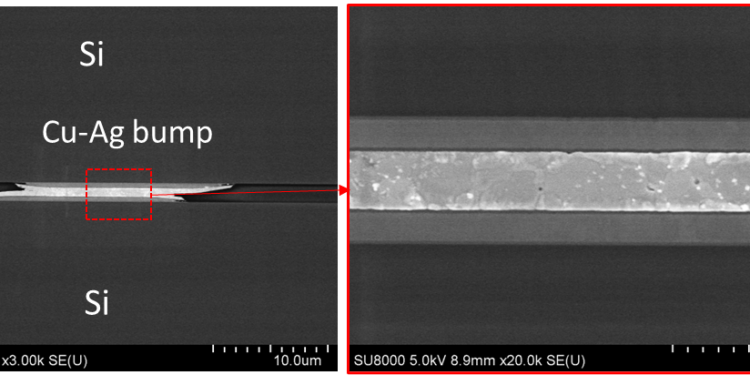

Today, a group of researchers at the University of Osaka showed how to attach a copper “bump” electrode directly to a silver coating. “Our process can be performed under mild conditions, at relatively low temperatures and without additional pressure, but the cords are able to withstand more than a thousand cycles of thermal shocks from -55 to 125 ° C,” said the first author Zheng Zhang. In this new method, silver is first applied to two copper surfaces to bond at room temperature. Heat is then applied to anneal the silver layers, causing the surface to undergo microscopic changes in a process called “stress migration.” The release of tension during annea leads to hardening of the surface and provides a sufficiently effective area between the two layers of silver. As a result, gluing can be applied without the use of pressure, even at relatively low annealing temperatures. A lasting connection of just 20 micrometers can be achieved in just ten minutes. This process requires only mild temperature (180 ° C) and can operate under atmospheric conditions.

The team was able to confirm the surface roughness of sputtered and annealed chips using scanning electron microscopy and atomic force microscopy images. “This technology is expected to contribute to high-density interconnect chips and advanced 3D packaging,” said lead author Katsuaki Suganuma.