Researchers from Tohoku University, the University of Messina, and the University of California, Santa Barbara (UCSB) have developed a large-scale probabilistic computer (p-computer) with stochastic spintronic devices (Spintronic computer that can perform well) that is suitable for difficult mathematical problems such as optimization integration with machines education.

Moore’s Law predicts that computers become faster every two years due to the evolution of semiconductor chips. Although this has happened throughout history, evolution continues to go backwards. Machine learning and human intelligence transformations require more advanced computing power. Quantum computing is one way to solve these challenges, but major obstacles to the realization of quantum computing may still remain.

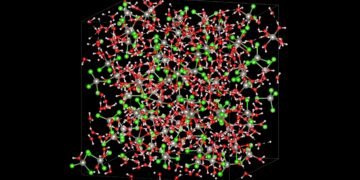

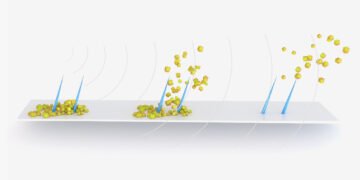

A p-computer uses a stochastic architecture called probabilistic bits (p-bits). Unlike traditional computer bits, p-bits oscillate between states. A p-computer can work indoors and work as a domain-specific computer for various applications in machine learning and artificial intelligence. Just as quantum computers try to solve quantum problems in quantum chemistry, p-computers try to overcome probabilistic algorithms, which are often used for complex computational problems and combining optimization and sampling.

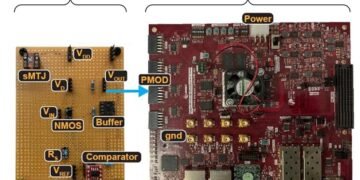

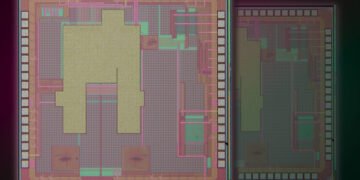

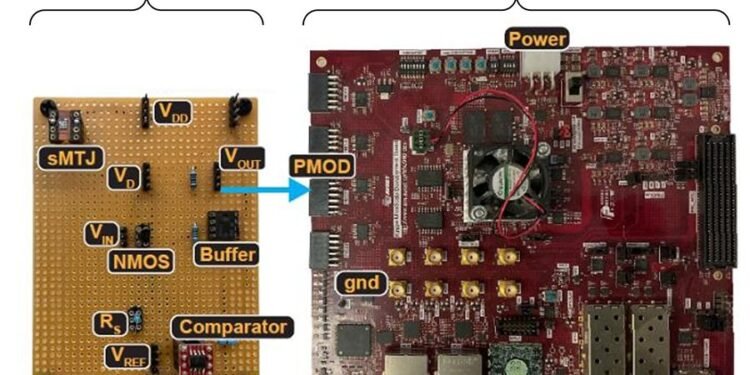

Recently, researchers from Tohoku University, Purdue University and UCSB have shown that p-bits can be efficiently obtained using highly tuned spintronic devices called stochastic magnetic tunnel junctions (sMTJs). Currently, p-bits based on sMTJ are applied in small sizes; and only a proof of concept of spintronic p-computing for collective optimization and machine learning is presented.

The research team presented two important breakthroughs at the 68th International Electronic Devices Conference (IEDM) on December 6, 2022.

Second, a probabilistic implementation of the quantum algorithm, Simulated Quantum Annealing (SQA), has been carried out on the p-computer “sMTJ+FPGA” with a systematic approach to complex optimization problems.

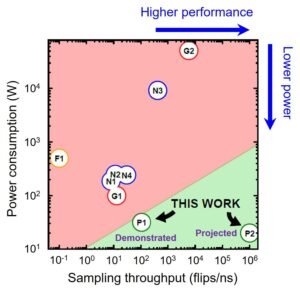

The researchers also compared the performance of p-computer sMTJ based on computer hardware, such as graphics processing units (GPUs) and tensor processing units (TPUs). They showed that the p-computer, using a high-performance sMTJ first showed that a team at Tohoku University, can achieve significant improvements in production and energy consumption in traditional technologies.

“Currently, the p”s-MTJ+FPGA” computer is a prototype with unique properties,” said Professor Shunsuke Fukami, a member of the research team. “In the future, embedded p-computers using magnetoresistive random-access memory (MRAM) technology that is compatible with semiconductor systems may be possible, but this will require a design process, and experts in materials, physics, design of circuits and algorithms. should be developed.”